Nytt timingverktøy

Cadence lanserer sitt nye Allegro TimingVision miljø, som de hevder vil gjøre timingarbeidet opptil 67% raskere.

Denne artikkelen er 2 år eller eldre

TimingVision blir tilgjengelig med Cadence Allegro PCB Designer, og skal gjøre det mulig for mønsterkortdesignere å spare mye tid når de skal sikre at signalene i et grensesnitt møter timingspesifikasjonene.

Ifølge Cadence blir dette en stadig viktigere egenskap etterhvert som datahastighetene øker og spenningene synker i dagens avanserte protokoller, som DDR3/DDR4, PCI Express, og SATA.

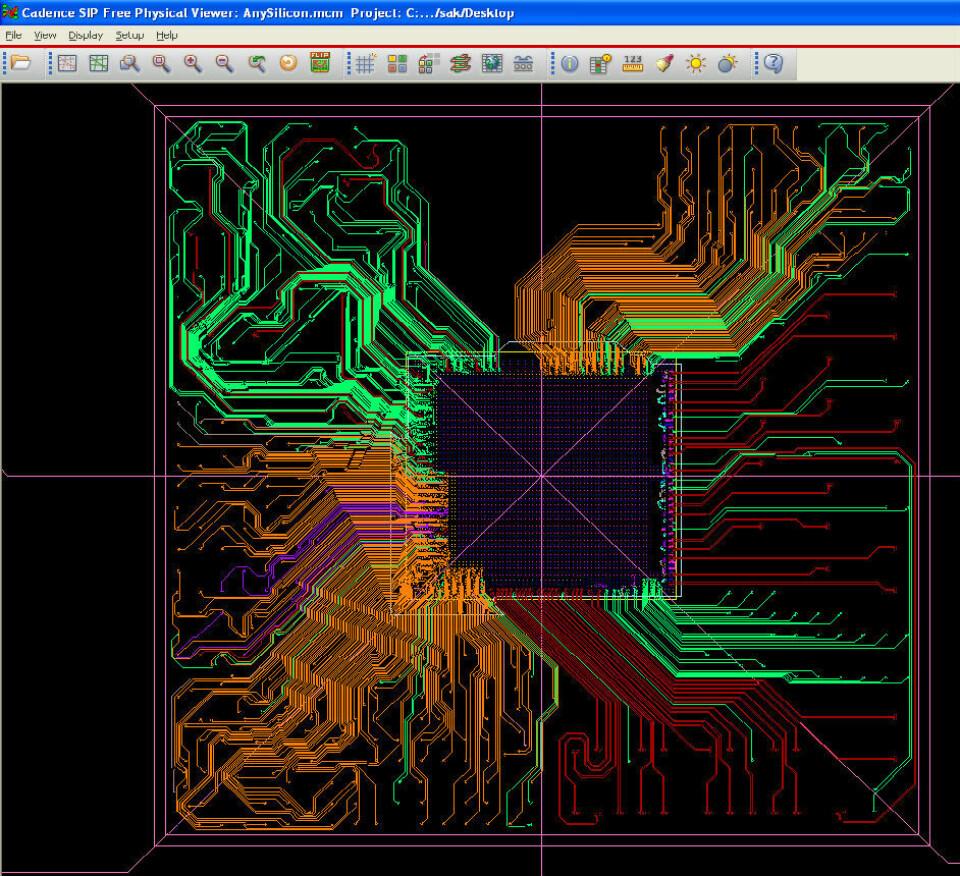

TimingVision benytter en innebygd timingmaskin for å analysere hele grensesnittstrukturen og utvikle timingmål for å hjelpe designeren å visualisere sanntids forsinkelse og faseinformasjon direkte på et utlegg.

Dette skal redusere manuell redigering, total implementeringstid og arbeidsinnsats, heter det. Kombinert med Cadence Sigrity effektfølsomme SI analyseverktøy, skal TimingVision miljøet muliggjøre rask implementering og finjustering i samsvar med standardgrensesnitt.

Noen av egenskapene er:

TimingVision miljø, som gir dynamisk tilbakemelding på aktive og relaterte signaler under redigering av utlegget.

Auto-interaktiv Fase Tuning (AiPT), for å kompensere både statiske og dynamiske begrensninger på et utvalgt sett av differensielle par

Auto-interaktiv Forsinkelsestuning (AiDT), for å kompensere for signalforsinkelse og begrensninger på total etselengde spesifisert i det fysiske designet, på et utvalgt sett av signaler, slik som en bytelinje.

TimingVision miljøet er nå, sammen med det auto-interaktive rutingmiljøet, tilgjengelig som del av Allegro PCB High-Speed Option.

Mer om TimingVision miljøet her.