MIPS-kjerne for FPGA

Første MIPS-baserte «myke» prosessorkjerne optimalisert for FPGA introdusert gjennom industrisamarbeid.

Denne artikkelen er 2 år eller eldre

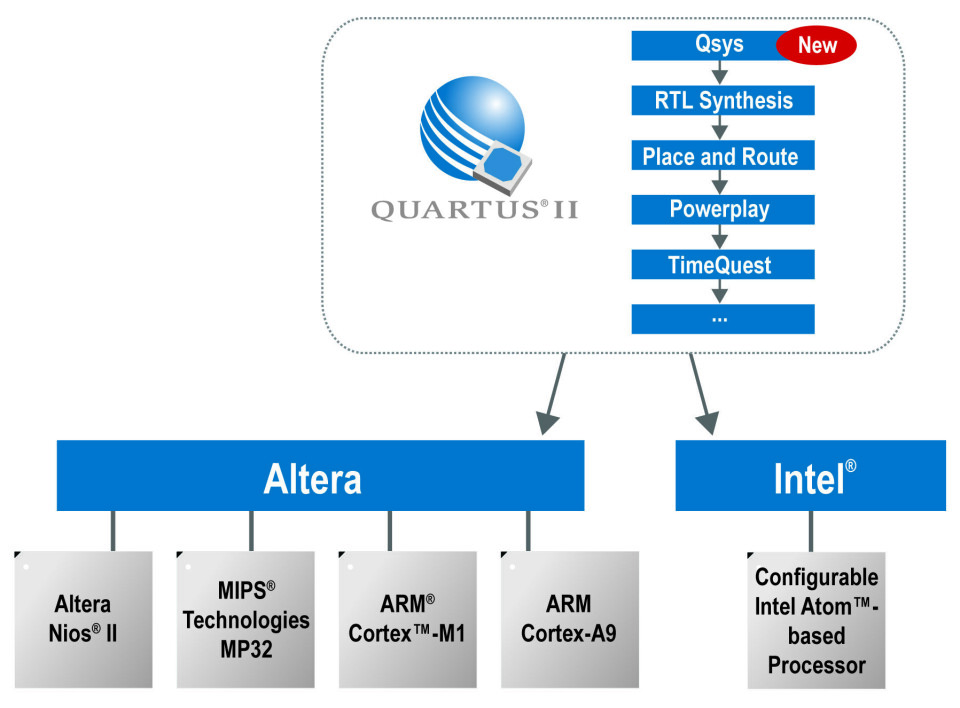

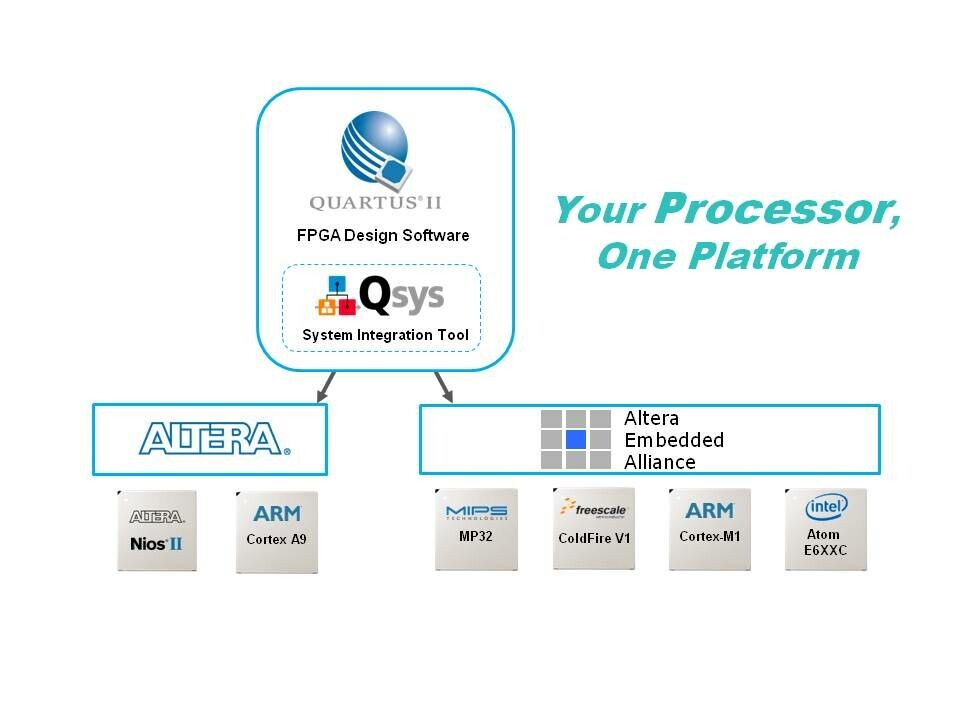

Altera, MIPS Technologies og System Level Solutions Corporation (SLS) lanserer nå en MIPS-basert myk prosessorkjerne som er optimalisert for FPGA og bruk med Alteras FPGAer og ASICs. Kjernen støttes dessuten av Wind Rivers VxWorks sanntids operativsystem (RTOS).

Den nye prosessoren med betegnelsen MP32 er en MIPS-kompatibel applikasjonsprosessor som drar med seg et stort økosystem med programvareutviklingsverktøy og operativsystemer.

MP32 skal også være den første FPGA-baserte prosessoren som støttes av VxWorks og MIPS Navigator ICS programvareutviklingssett. Sammen med Alteras store utvalg av innvevde IP-kjerner, nye designverktøy med mer, regner leverandørene med at prosessoren skal være egnet for utvikling av fleksible, énbrikkeløsninger for bruk innen nettverk, video- og digitale signalprosesseringsapplikasjoner.

– MP32-prosessoren har en arkitekturbasert fleksibilitet som muliggjør flerkjernedesign med en sømløs designflyt, kommenterer markedsdirektør Art Swift i MIPS Technologies. – De som designer MIPS-Based systemer kan dessuten benytte kjente verktøy og programmer, og velge den plattformen som passer best, enten det er FPGA, HardCopy ASIC eller standardcelle ASIC.

Prosessorkjernen distribueres og støttes gjennom Altera Embedded Alliance partneren SLS. De bidrar med omfattende IP-portefølje, systemkunnskap og designerfaring for å ta frem bruksklare MP32 prosessorbaserte løsninger.