Blikk på avansert halvlederpakking

Avansert halvlederpakking baner vei for datasentrisk fremtid, ifølge IDTechEx.

Denne artikkelen er 2 år eller eldre

Hvis fremtiden skulle kategoriseres i ett ord, ville den vært «datasentrisk», skriver tekno-analytikeren Dr Yu-Han Chang i en ny rapport om halvlederpakking. I flere tiår har IC-leverandører designet brikker som har alle funksjoner integrert på samme brikkekjerne. Skalering av monolittiske ICer blir imidlertid vanskeligere og mer kostbart samtidig som industrien ser en utflating av Moores lov. IC-leverandører har blitt tvunget i retning "avansert halvlederpakking" for å møte verdens databehov.

I dag ser vi en eksplosjon av data på alle nivåer og i nesten alle bransjer. Hvert sekund genererer den digitale verden 4000 terabyte med data, og denne mengden forventes å øke betraktelig i fremtiden. Datarike applikasjoner som maskinlæring og AI er de viktigste datadriverne i et bredt spekter av applikasjoner, inkludert datasentre, 5G og autonome kjøretøy. Det kreves en kraftig prosessor for å kjøre disse appene, der grunnlaget er en integrert krets (IC) basert på silisium (Si).

Hva er avansert halvlederpakking?

Prosessen med pakking av halvledere spiller en nøkkelrolle i halvlederproduksjon og -design. For eksempel, i IC-pakkingsprosessen, er den nakne IC-brikken innkapslet i en støttende kapsling med elektriske kontakter. Kapslingen beskytter den nakne IC-brikken mot fysisk skade og korrosjon og kobler ICen via et kretskort til andre enheter. Halvlederpakking har eksistert i flere tiår – den første volumproduksjonen av halvlederpakker kom på begynnelsen av 1970-tallet. Så, hva er nytt?

Som nevnt, på grunn av oppbremsingen i Moores lov og de økende kostnadene ved å produsere en monolitisk IC, trengte leverandørene nye designtilnærminger for å muliggjøre kostnadseffektive prosessorer med høy ytelse. Et nytt design kalt «brikkebit», eller "chiplet" er nøkkeltrenden fremover.

Ideen bak brikkebiter er å "dele" en monolittisk IC i flere funksjonelle blokker, rekonstituere funksjonsblokkene til separate brikkebiter, og deretter "remontere" disse på pakkenivå. Ideelt sett bør en prosessor basert på brikkedesign ha samme eller høyere ytelse, men lavere totale produksjonskostnader enn en monolitisk IC. Pakkemetoder, spesielt de som brukes til å koble sammen flere brikker, spiller en avgjørende rolle i brikkedesign siden de påvirker systemets ytelse som helhet.

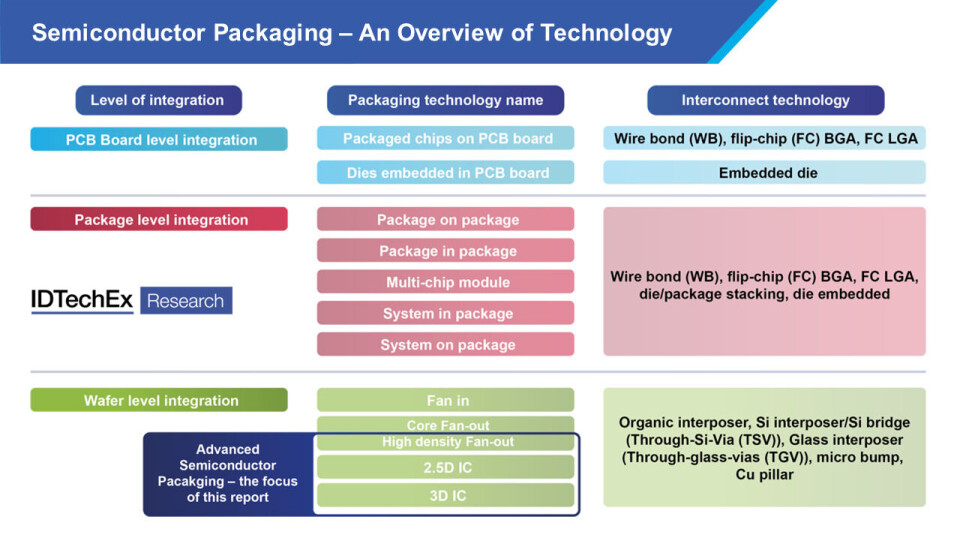

Disse pakketeknologiene, inkludert 2,5D IC, 3D IC og pakking på skivenivå med høytetthets fanout, er kategorisert som "avansert halvlederemballasje" og er tema for IDTechEx sin nylig utgitte forskningsrapport "Advanced Semiconductor Packaging 2023-2033". Metodene tillater sammenslåing av flere brikker med forskjellige prosessnoder på et enkelt substrat, og har små terminalstørrelser for å muliggjøre høyere sammenkoblingstettheter og høyere integrasjonsmuligheter.

Den nye IDTechEx rapporten skal inneholde en detaljert gjennomgang av de nyeste fremskrittene innen avanserte pakketeknologier for halvledere, viktige tekniske trender, analyser over hele verdikjeden, analyser av store aktører, og detaljerte markedsprognoser.