Mikrokontrollere:

Renesas går RISC-V

Renesas lanserer første generasjon av sin egen 32-bit RISC-V CPU kjerne, og ligger dermed godt foran i løypa.

Denne artikkelen er 2 år eller eldre

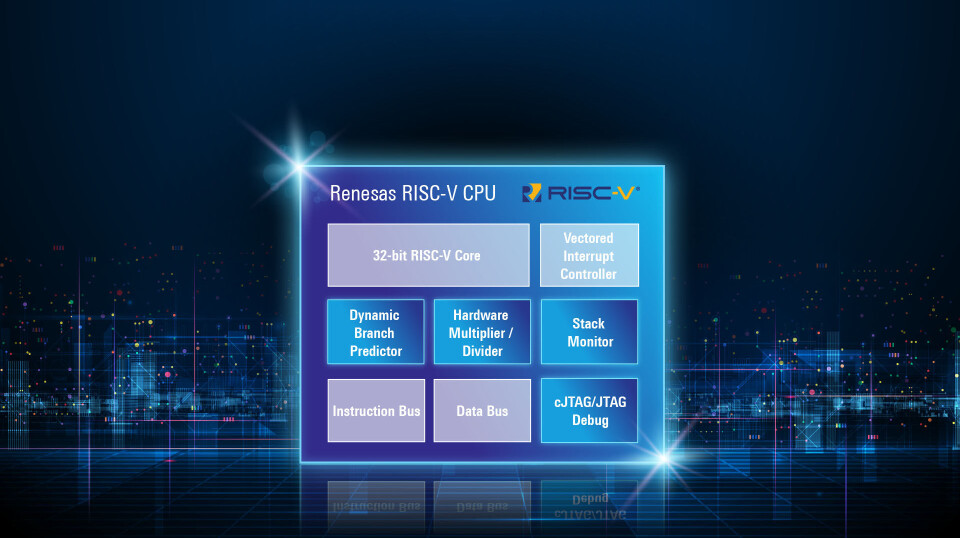

Renesas Electronics Corporation kunngjorde i dag at de har designet og testet en 32-bits CPU-kjerne basert på den åpne RISC-V instruksjonssettarkitekturen (ISA).

Renesas er dermed blant de første (store) i bransjen som uavhengig utviklet en CPU-kjerne for 32-biters generelle RISC-V-markedet . Løsningen skal gi en åpen og fleksibel plattform for IoT, forbrukerelektronikk, helseteknologi og industrielle systemer, opplyser selskapet.

Den nye RISC-V CPU-kjernen vil utfylle Renesas eksisterende IP-portefølje med 32-bits mikrokontrollere (MCU), inkludert den proprietære RX-familien og RA-familien basert på Arm Cortex-M-arkitekturen.

RISC-V er en åpen ISA som raskt vinner popularitet i halvlederindustrien på grunn av sin fleksibilitet, skalerbarhet, energieffektivitet og åpne økosystem. Mens mange MCU-leverandører nylig har opprettet felles investeringsallianser for å akselerere utviklingen av RISC-V-produkter, har Renesas allerede utviklet en ny RISC-V-kjerne alene.

Denne allsidige CPU-en kan tjene som en hovedapplikasjonskontroller, en komplementær sekundær kjerne i SoCer, on-chip-undersystemer eller til og med i dypt innvevde ASSPer. Dette posisjonerer Renesas helt i front i det fremvoksende RISC-V-markedet, etter tidligere introduksjoner av sine 32-bits stemmestyrings- og motorstyrings- ASSP, samt RZ/Five 64-bits mikroprosessorer for generell bruk (MPUer), som ble bygget på CPU-kjerner utviklet av Andes Technology Corp.

Lanseringen utløste gratulasjoner fra Calista Redmond, CEO i RISC-V International. – Denne prestasjonen eksemplifiserer hvordan RISC-V-økosystempartnere, som Renesas, raskt fremmer RISC-V-innovasjon. Vårt RISC-V-fellesskap spenner nå over 70 land med mer enn 4000 medlemmer, og vi venter ivrig på ytterligere innovasjoner som dukker opp fra dette dynamiske, ekspanderende markedet, sier hun.

Renesas’ RISC-V CPU oppnår en imponerende ytelse på 3,27 CoreMark/MHz, og overgår dermed lignende arkitekturer på markedet. Den inkluderer ifølge selskapet utvidelser for å forbedre ytelsen, samtidig som kodestørrelsen reduseres.

Renesas prøveproduserer komponenter basert på den nye kjernen til utvalgte kunder, med planer om å lansere sin første RISC-V-baserte MCU og tilhørende utviklingsverktøy i første kvartal 2024. Detaljer om den nye MCU vil bli publisert på det tidspunktet. Mer informasjon om RISC-V-løsninger er tilgjengelig på: renesas.com/risc-v.

En bloggartikkel om den nye RISC-V CPUen finner du her.