Designmetodikk:

UVVM – raskest voksende og støttet av romindustrien

Det åpne verifikasjonssystemet UVVM brukes snart av en tredel av alle FPGA-designere i verden, og har fått betydelig oppbakking av den europeiske romorganisasjonen ESA.

UVVM (Universal VHDL Verification Methodology) er en gratis og åpen kildekode-metodikk og et bibliotek for effektiv VHDL-verifisering av FPGA og ASIC – og skal også gi betydelig kvalitetsforbedring. Ifølge metodikkens «far», Espen Tallaksen, er UVVM fortsatt et av de raskest voksende verifikasjonssystemene, og hele 27 % av alle FPGA-designere verden over bruker løsningen (ref. Wilson Research, 2024).

ESA-interesse

Og som antydet i overskriften, er det spesielt spennende at den europeiske romorganisasjonen ESA har fattet interesse for metodikken. – Det første prosjektet med ESA fikk vi i 2017, forteller Tallaksen. – Gjennom Romsenteret fikk vi et møte med ESA-folk, som umiddelbart ble begeistret for UVVM. Dermed var det gjort. Siden har vi hatt et godt samarbeid med ESA, og gjennom det fått mange gode innspill til videreutvikling og nye funksjoner i UVVM. Ikke minst var den økonomiske støtten viktig, påpeker han. UVVM var jo i stor grad tuftet på eget engasjement og interesse.

Åpen kildekode

I disse dager er det omkring 20 år siden forløperen til UVVM ble påbegynt i daværende Digitas. Etter at Digitas ble kjøpt opp startet arbeidet på nytt i Bitvis AS, som utviklet det de kalte Bitvis Utility Library, i 2014 omdøpt til UVVM og gjort til åpen kildekode. Som kjent har det vært nye oppkjøp og knoppskytinger siden den gang, og i dag vedlikeholdes og videreutvikles kildekoden i fellesskap av EmLogic og Inventas – fremdeles med Espen Tallaksen som prosjektleder

Godt samarbeid

I mars i fjor startet det tredje samarbeidsprosjektet med ESA, der EmLogic står som primærleverandør. Også her samarbeider man med Inventas. – Vi har et utmerket teknisk samarbeid med dem, og har ukentlige oppdateringsmøter om UVVM, sier Tallaksen. Det nåværende ESA-prosjektet skal sluttføres i år, men alt ligger til rette for at en søknad om utvidelse går i orden.

Ustrukturerte testbenker

– Bakgrunnen for å utvikle et effektivt verifikasjonssystem var i begynnelsen delvis av markedsføringshensyn, og delvis ren entusiasme, sier Tallaksen. Utgangspunktet var frustrasjon over eksisterende testbenker for FPGA, som gjerne var ustrukturerte og med dårlig arkitektur. Noe som blant annet gjorde det utfordrende å gå inn i en annens testbenk og forstå hva som var gjort. Eller enda verre, å gjøre endringer.

Mangelfull dekning

Verifikasjon av komplekse strukturer fører typisk til komplekse testbenker, som også kan gjøre det vanskelig å tvinge designet inn i krevende «hjørnetilfeller», altså oppgaver som utfordrer designets kapasitet. For eksempel kan det være vanskelig å styre mange grensesnitt samtidig. Hver for seg kan de fungere fint, men når mye skjer samtidig kan det også oppstå feil.

Effektivt

– Med UVVM kan du lage en god arkitektur som er både forståelig og systematisk. Ved å lese kommandolinjene i en testsekvenser, skal du enkelt kunne forstå hva som skjer, forteller Tallaksen. – Det er mye å hente på effektivisering. Ifølge Wilson Research brukes 50 % av utviklingstiden på verifikasjon. Og nesten halvparten av verifikasjonstiden brukes på debugging.

«Håpløst»

– Å bruke 25 % av prosjekttiden på debugging høres helt håpløst ut, men skyldes i stor grad at testbenkene ikke er gode nok, og at også testbenken blir vanskelig å debugge når den er vanskelig å lage. Men ved å bruke en høy-nivå testsekvenser med klare kommandoer kan du spare mye: Bedre oversikt, mer effektiv debugging og ikke minst, bedre kvalitet, understreker Tallaksen.

Kvalitet

Kvalitet er selvsagt viktig, ikke minst i romprosjekter. I UVVM fins det mange funksjoner for å sjekke kvalitet, f.eks. kravsporing (requirements tracking). Der tar man utgangspunkt i en liste med krav som skal oppfylles i testbenken, og som kan krysses av når de er sjekket. Til slutt kan man lage en oppsummering av kravdekningen som gir full oversikt og som dessuten kan brukes til å dokumentere kvalitet.

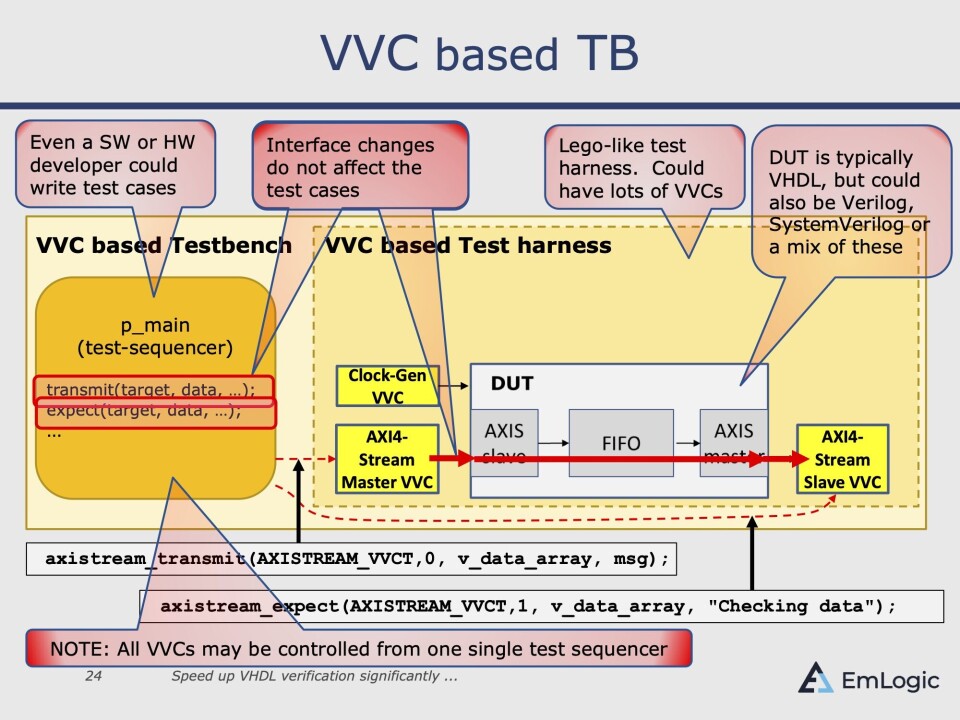

Lego-prinsipp

Det er mange deler i UVVM, og det er kommet til mange utvidelser, slik som dekning av funksjonelle scenarier og spesielle testdekninger. Oppbygging av UVVM-testbenker har en lego-lignende tilnærming under oppkobling av verifikasjonskomponenter, og ifølge Tallaksen kan både programvare- og maskinvareingeniører enkelt skrive testtilfeller.

Videreutvikling

Systemet er under stadig videreutvikling, og en av de nyere funksjonene som er lagt inn, er en funksjon som oppdager uventede hendelser. Det vil si at man ikke bare sjekker f.eks. en utgang når det forventes et resultat etter en kommando. Funksjonen vil også oppdage om en modul sender ut data eller endrer på grensesnitt-signaler når man ikke forventer det. En annen ny funksjon er «completion detection», som sjekker at alle komponenter er ferdig med det de skal gjøre. Og stadig flere påbygginger kommer.

Enkelt å komme i gang

– Det er fullt mulig å bruke kun de enklere delene av UVVM, alt etter hvor komplekst designet er, og hva man trenger. Når det gjelder kvalitetssjekk, kan det uansett lønne seg å bruke UVVM – også helt basis funksjoner, sier Tallaksen, som mener det skal være enkelt å komme i gang på et lavere nivå. EmLogic tilbyr kurs, men det ligger også mye informasjon og webinarer på nett for de som er interessert. I tillegg holdes det gjesteforelesninger på flere universiteter, bl.a. i Bergen og Trondheim.