Utvikling av kraftomformere:

Fordeler ved UL-sertifiserte smarte gatedrivere i avanserte kraftomformere

Høyere svitsjehastigheter og nye materialer kan forbedre effektiviteten i kraftomformere – men det krever også optimalisering av kretsene rundt selve svitsjene.

Denne artikkelen er 2 år eller eldre

Gjennom forbedringer i svitsjer og mikrokontrollere

kan designere av kraftelektronikk forbedre effektiviteten med opptil

ytterligere ett prosentpoeng for hver nye produktgenerasjon de designer. Og det

er ingen grense for antall applikasjoner som kan dra nytte av disse

fremskrittene, fra elektriske kjøretøyer (EV) med vekselrettere og

batteriladere, til avbruddsfri strømforsyning (UPS), servomotorer og

solcelleomformere.

Imidlertid krever disse forbedringene ofte overgang til høyere svitsjehastigheter og endring fra silisium IGBT eller MOSFET til silisiumkarbid (SiC) komponenter. Dette introduserer nye utfordringer som må løses når ingeniører utforsker virkningen av økt dv/dt og di/dt rundt svitsjene.

Krever optimalisering

Ulike tilnærminger for å løse slike problemer krever at de elektroniske kretsene rundt svitsjene er optimalisert. Utfordringene spenner fra effekten av uønsket innkobling forårsaket av den ikke-lineære Miller-kapasitansen mellom kollektor/drain og gate, til å reagere på kortslutninger i eller overbelastning av svitsjene. Samtlige løsninger på disse problemene tar tid å bestemme, løse og kvalifisere. I stedet er det ofte fordelaktig å velge en integrert smart gate-driver som allerede har UL/cUL-sertifisering.

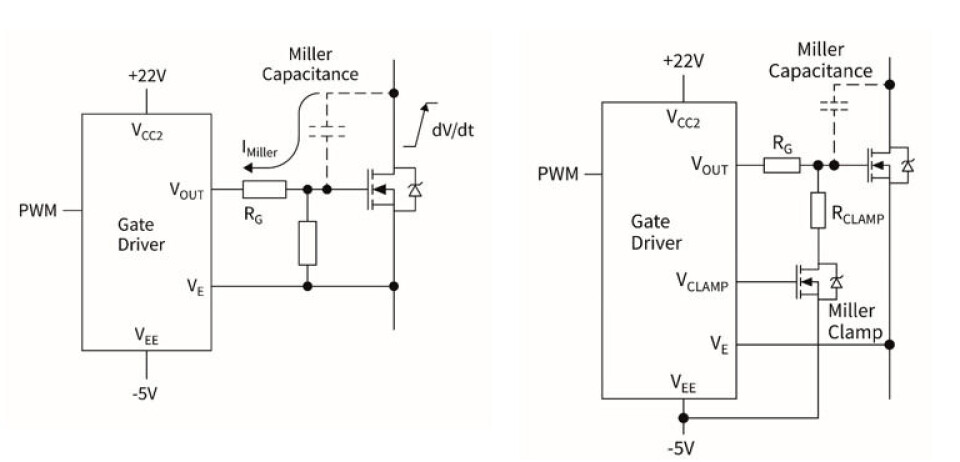

Håndtering av Miller-kapasitans

Når svitsjene slås av, injiserer Miller-kapasitansen mellom kollektor/drain strøm inn i gaten. Enhver seriemotstand mellom gaten og drivkretsen resulterer i at det utvikles en spenning som i verste fall kan føre til at svitsjen slås på igjen. Så selv om IGBTer og Si/SiC-MOSFETer nominelt er av for en VGS eller VGE på 0V, bruker gatedriverkretser ofte en lavere, negativ spenning når de påtrykker av-tilstanden (Figur 1, venstre). Dette varierer fra -5V for MOSFET-er til -7V for IGBT-er, og motvirker dermed enhver gate-motstand-indusert spenningsøkning.

Selv om dette er en helt akseptabel løsning på problemet, krever det en ekstra forsyningsskinne som kanskje ikke er nødvendig i resten av designet. For å unngå dette kan en Miller-klemmekrets brukes. Ved å introdusere en ekstra MOSFET mellom gaten og senderen/source, klemmes gatespenningen etter at drivsignalet har gått under et forhåndsbestemt nivå (Figur 1, høyre). Etter at kollektor/drain har stabilisert seg på sin av-tilstand spenning, kan denne klemsvitsjen kobles ut. Tidspunktet for dette trinnet er ikke spesielt kritisk, men det må ha blitt fullført før neste på-tilstand.

Beskyttelse mot overbelastningstilstander

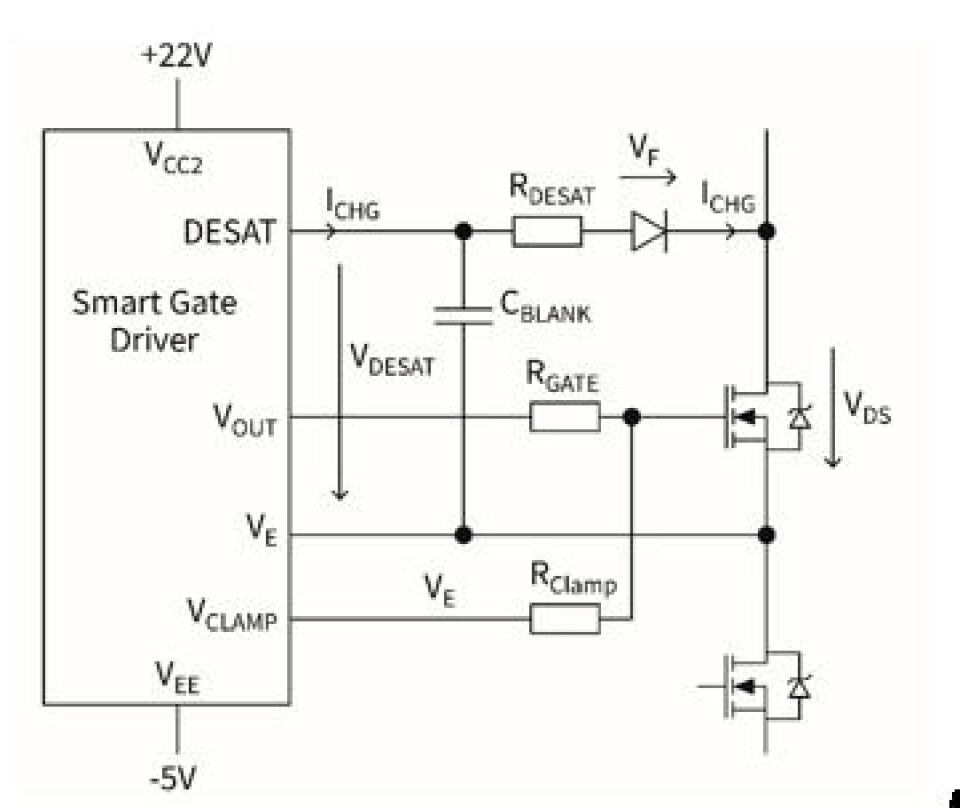

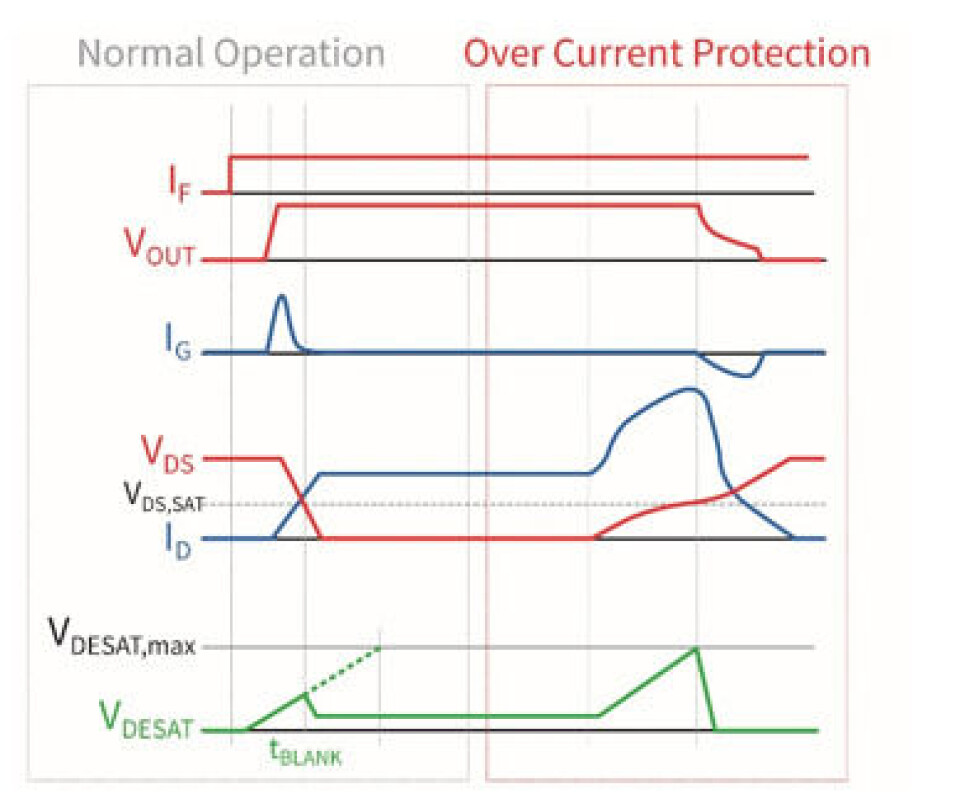

Kraftsvitsjer kan svikte når de utsettes for kortslutninger eller når den påførte gatedriverspenningen ikke klarer å presse dem helt inn i metningsområdet. Overvåking av kollektor-/drainspenningen under på-tilstand gjør at driverkretsen kan tvinge svitsjen tilbake til av-tilstand dersom en forhåndsdefinert terskelspenning overskrides. Denne teknikken er kjent som avmetning (de-saturation - DESAT). Fordi motstandstidene mot kortslutning er svært korte (i beste fall noen få millisekunder), må denne mekanismen reagere veldig raskt. Dette er imidlertid svært utfordrende med komponenter som svitsjer med mange kHz og i et elektrisk støyende miljø.

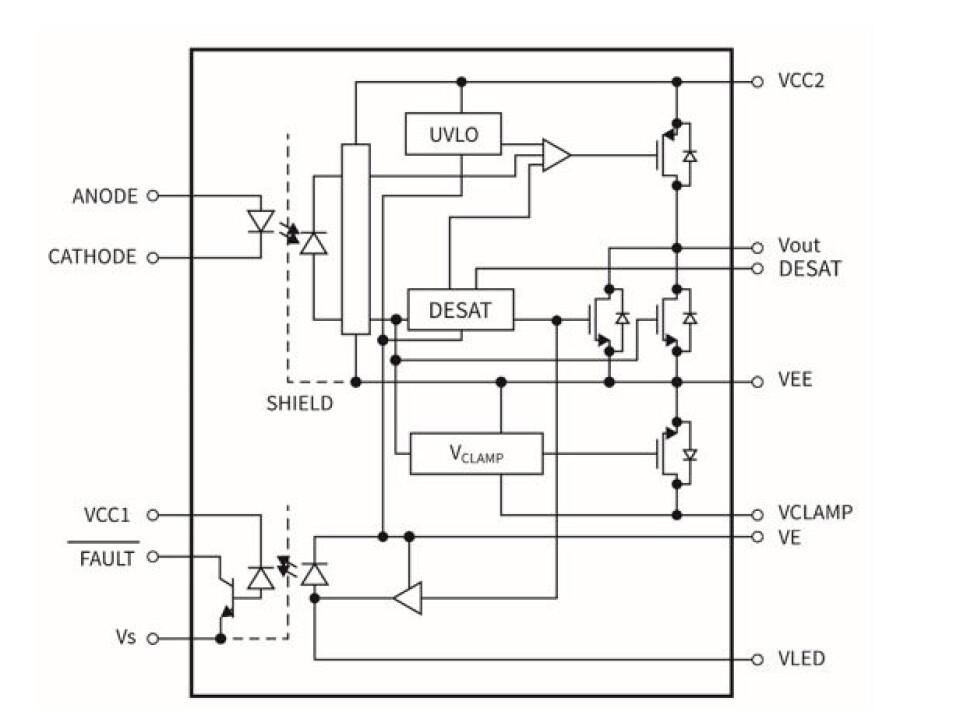

Integrerte gatedrivere med en DESAT-funksjon krever et minimalt antall tilleggskomponenter for å implementere slik beskyttelse. I kombinasjon med et motstand-kondensatornettverk kobles en diode til kollektor/drain på den ene siden og gatedriverens DESAT-pinne på den andre (Figur 2). Når kraftenheten er mettet, er dioden forspent, og trekker DESAT-pinnen lavt. Ved å sammenligne denne spenningen med portdriverens VDESAT,max -innstilling og drivertilstand, kan gatedriveren fastslå om det har oppstått en feiltilstand.

Dioden må klassifiseres for hele DC-bussen pluss en

viss margin, som fort kan nå 1000V eller mer i noen applikasjoner, selv om fremoverstrømmen

kan være lav. Enheten skal også være hurtigvirkende med svært lav kapasitans og

omvendt gjenopprettingslading. Fordi disse egenskapene er vanskelige å finne i

en enkelt diode, kombineres enheter ofte i serie. Dette bidrar til å øke

spenningsklassifiseringen samtidig som kapasitansen reduseres, men øker

spenningsfallet fremover og i sin tur DESAT-terskeldeteksjonen. SiC-dioder er

også et alternativ, men det bør huskes at de har høyere fremoverspenning enn

konvensjonelle silisiumdioder.

For å beskytte DESAT-pinnen er en Zener-diode det ideelle valget for å klemme spenningen til et nivå som er trygt for gatedriveren, mens en Schottky-diode kan klemme signalet under jord.

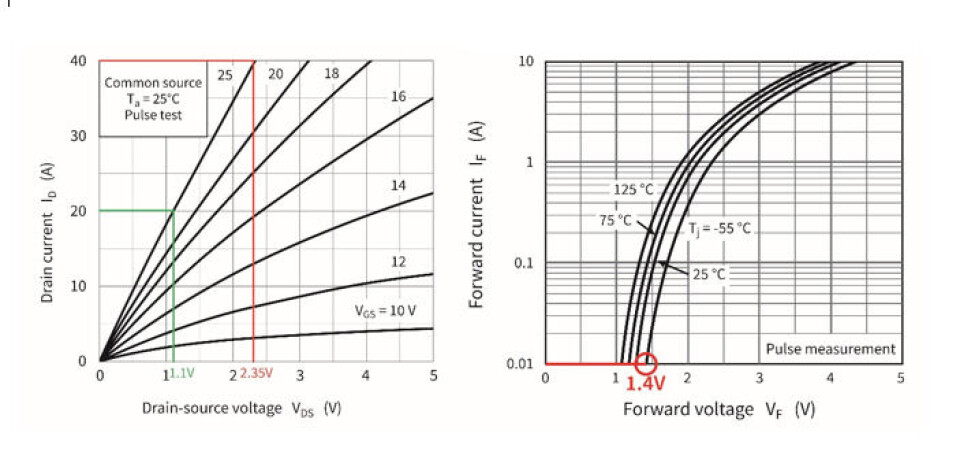

Bestemmelse av komponenter for DESAT-kretser

For å begynne å designe DESAT-kretsen, må overføringskarakteristikken til MOSFET fastslås. Herfra kan motstanden og kondensatoren for DESAT-kretsen beregnes. For eksempel, ved å undersøke ID – VDS kurven for en SiC MOSFET, bestemmes drain-source-spenningen for det normale og maksimale driftspunktet for en fast VGS (Figur 3, venstre).

I tilfellet med en TW070J120B, er VDS 1,1 V

ved en ID på 20 A, og VDS er 2,35 V ved en maksimum ID

på 40A.

Neste steg er å finne VF for de valgte diodene. For to CRF03A dioder med rask gjenoppretting, er denne 2 × 1,4 V som vist i Figur 3 (til høyre).

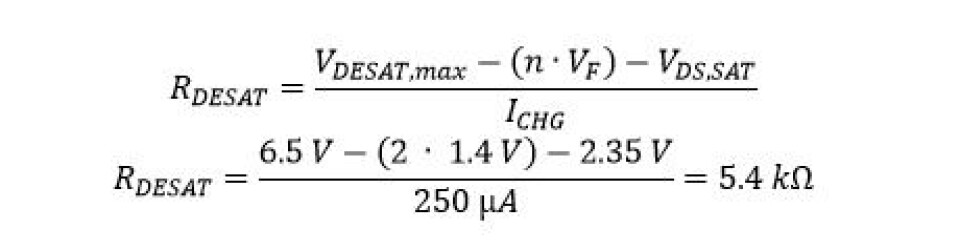

Siste steg er å bestemme VDESAT,max og ICHG fra databladet til den valgte smarte gatedriveren. For Toshiba TLP5214A er dette henholdsvis 6,5 V og 250 µA. Ut fra dette kan RDESAT beregnes (Figur 4).

Alt som gjenstår nå, er å beregne kapasitansen for CBLANK.

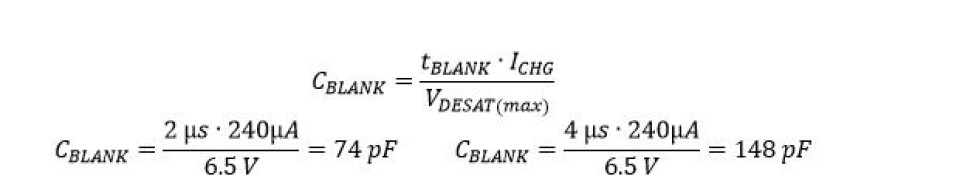

Ved å bruke kortslutningsmotstandstidene til den valgte SiC MOSFETen, som er

mellom 2 µs og 4 µs, kan dette bestemmes som i Figur 5.

Under drift vil kortslutning- og

overstrømbeskyttelsen reagere som vist i Figur 6.

Smart gate-drivere som TLP5214A genererer et isolert signal via en feilutgangspinne, som indikerer problemet til kontrollerkretsen når den myke avstengningen er aktivert (Figur 7). Kontrolleren kan deretter bestemme den beste handlingen, for eksempel å forsøke å slå på kraftsvitsjen etter en programmert forsinkelse for å sikre at den gjennomsnittlige effektdissiperingen ikke er for stor.

Skulle tidsperiodene for DESAT-blanking og myk avstengning være for lange for applikasjonen, kanskje fordi toppbelastning og støy er lavere, kan designere vurdere TLP5214, som i hovedsak tilbyr de samme egenskapene, men med kortere timing for disse to parameterne. Begge enhetene gir en maksimal ±4,0 A topp utgangsstrøm og har en skinne-til-skinne utgangssving. For applikasjoner med lavere maks strømkrav for gatedriver, eller hvis bakoverkompatibilitet med tidligere gatedrivere er nødvendig, har man tilgjengelig TLP5212, som tilbyr en maksimal ±2,5 A topp utgangsstrøm og ikke-skinne-til-skinne sving.

Med tilgjengelighet i en SO-16L pakke ivaretas

krympe- og klaringsavstand på 8mm. Isolasjonsspenningen på an 5.000 Vrms(min)

gjør denne familien med smarte gatedrivere egnet for systemspenninger på 600VAC, samtidig som den

møter sikkerhetsstandardene UL 1577 og

EN 60747. For IGBTer støttes svitsjefrekvenser opp til 50kHz mens SiC MOSFETs kan

drives med opp til 650kHz. Forsinkelsesforplanting er på ±150ns for TLP5212 og

±80ns for TPL5214 og TLP5214A. For å støtte høyere gatestrømmer tilbys TLP5231 som

en smart gate pre-driver, og som gjør designteamene i stand til å spesifisere

deres gatedriver-MOSFETs i henhold til applikasjonskravene.

Smarte gatedrivere som forenkler design av kraftelektronikk

Bruk av diskrete komponenter, håndtering av feildeteksjon og virkningen av Miller-kapasitans i kraftdesign er mulig. En slik tilnærming krever imidlertid kortplass og mange komponenter, sammen med tid til å teste og optimalisere designet. Designet vil også kreve sikkerhetssertifisering. Smart gate-drivere integrerer alle nødvendige kretser som trengs for DESAT-feilhåndtering og -deteksjon, samtidig som de unngår behovet for negativ forsyning, takket være Miller-klemmeevnen. Med utvalget av sikkerhetssertifiserte gatedrivere som er omtalt her, gis skalerbar støtte for et bredt spekter av kraftbehov både for tradisjonelle IGBT- og silisium-MOSFET-design og for de som går over til høyhastighetssvitsjing ved bruk av SiC MOSFETer.

Om forfatteren: Dr.-Ing Matthias Ortmann er sjefingeniør hos Toshiba Electronics Europe GmbH.