Innvevd SRAM fungerer på 0,5V-1,0V

Toshiba utvikler kretsteknikker for innvevd SRAM som fungerer med store spenningsvariasjoner, og helt ned til 0,5 volt.

Denne artikkelen er 2 år eller eldre

Toshiba Corporation meddeler at de har utviklet kretsteknikker for innvevd SRAM som vil vøre i stand til å operere i et stort spenningsområde, fra 0,5 V til 1,0V. Dette mener de skal bidra effektivt til lavere strømforbruk.

Ifølge Toshiba kan teknikkene medføre 57% lavere strømforbruk og redusert cellefeilrate.

Testbrikken de nå har produsert er laget med tre nye teknikker som skal sikre pålitelig drift av SRAM, selv når driftsspenningen varierer. Samtidig skal cellefeilraten være redusert, og man har oppnådd rask operasjon.

Teknikken er implementert i en 40nm 2Mb SRAM testbrikke, som Toshiba har demonstrert fungerer ved 0,5 V.

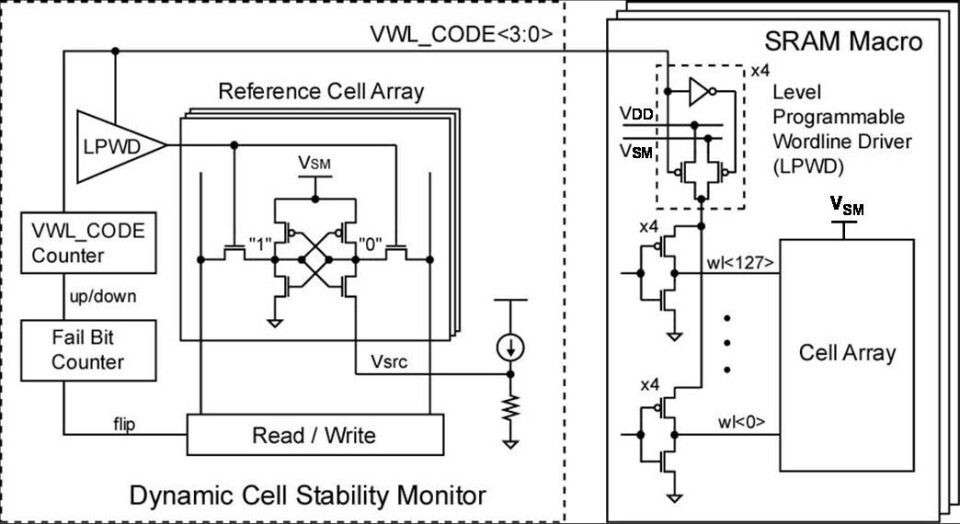

Innvevde SRAM i halvlederkomponenter for mobilutstyr har flere celler for datalagring, og må ha stabil ytelse selv om cellekarakteristikkene varierer. Konvensjonelle SRAM-teknikker anvender velgersignaler for ordlinjer for lese-/skriveoperasjoner. Ettersom driftsforholdene, som transistorterskler, temperatur og spenning varierer, vil den optimale ordlinjespenningen som hver SRAM-celle vil fungere skikkelig med også endre seg. Den nye kretsteknikken skal imidlertid kunne forutse feilraten i SRAM-cellene i sanntid, og automatisk programmere ordlinjespenningen slik at celleminnet opprettholdes selv om driftsforholdene varierer. Resultatet skal være en reduksjon i feilraten som er en hundredel av tilsvarende konvensjonelle SRAM.

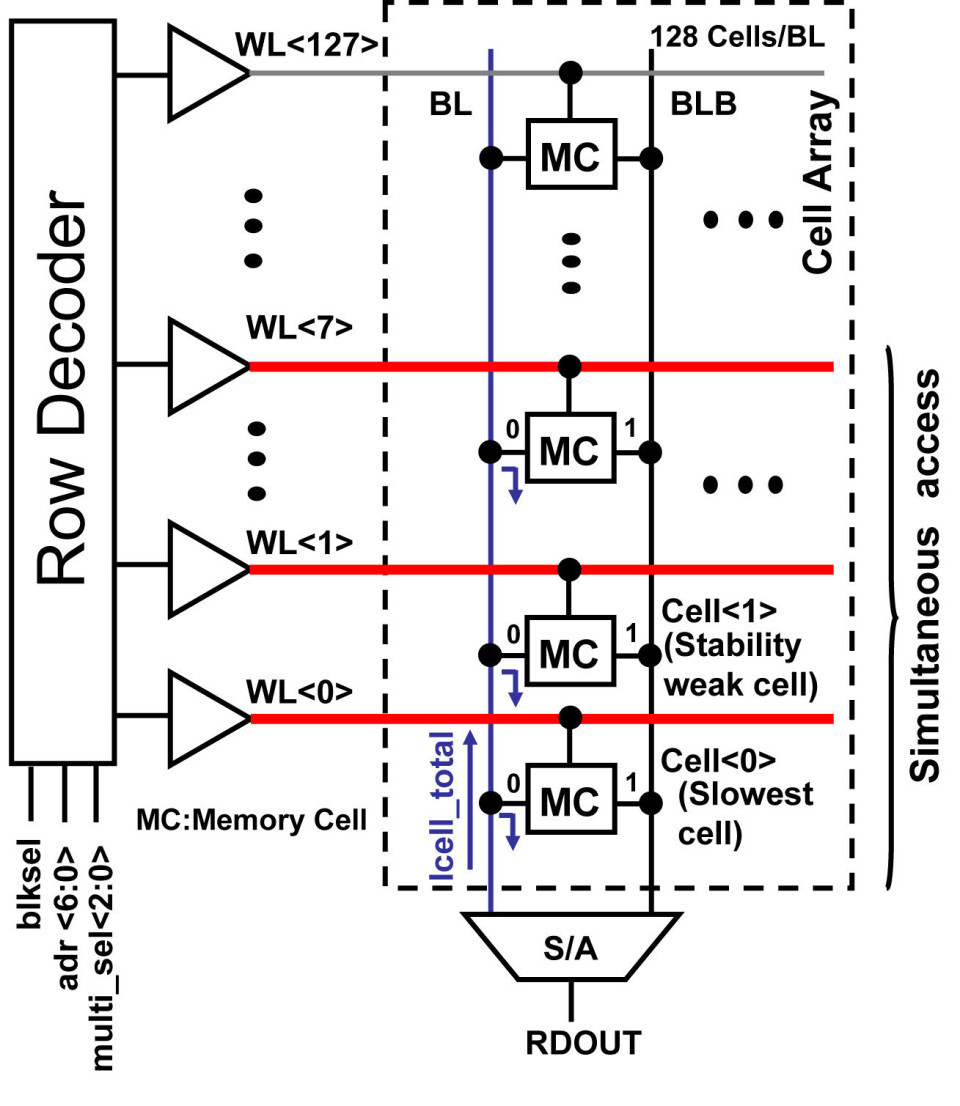

Når timing av aktiveringen av følerforsterkeren justeres til den langsomste cellen under lavspenningsfunksjon, vil den bli for langsom under høyere spenninger, noe som fører til at hele SRAMen blir for langsom. Den nye teknikken styrer ordlinjespenningen slik at spenningskarakteristikken til styrekretsen, som bestemmer timingen av aktivering av følerforsterkeren, tilpasses den langsomste cellens spenningskarakteristikk. Dermed er aktivering ved optimal timing mulig ved enhver driftsspenning, hevder Toshiba. Denne teknikken skal forbedre aktiveringstimingen under drift ved høyere spenning, selv om aktiveringen av følerforsterkeren er optimalisert ved den laveste driftsspenningen, noe som skal resultere i en forbedring av driftsfrekvensen på 18%.

Et annet problem har vært økt feilrate for SRAM-celler påvirket av bitlinjer i lese-/skriveoperasjoner ved lav spenning, som under 0,7 V. Mens konvensjonell teknikk velger ordlinjer en og en, kan den nye teknikken aktivere åtte ordlinjer samtidig for å lese/skrive de samme data, og dermed oppnå full funksjon ved spenninger ned til 0,5 V. Imidlertid blir den tilgjengelige minnekapasiteten da noe redusert.