Nytt designprogram for FPGA

Lattice Semiconductor Corporation lanserte nylig versjon 2.0 av sitt Diamond designverktøy, som også utgjør flaggskipet i deres designmiljø for Lattice FPGA produkter.

Denne artikkelen er 2 år eller eldre

Versjon 2.0 har avansert støtte for den nye FPGA-familien LatticeECP4, som er rettet mot kost- og effektsensitive applikasjoner innen trådløs og ledningsbasert kommunikasjon, video og databehandling.

Den nye versjonen hevdes å forbedre den totale brukeropplevelsen ved å muliggjøre raske bestemmelser av timing, og kommer med en ny, partisjonsbasert inkrmentell designflyt for LatticeECP3 FPGA komponenter.

Denne nye designflyten skal bl.a. hjelpe brukere å opprettholde designytelse og samtidig redusere kjøretiden etter at en designendring er gjort.

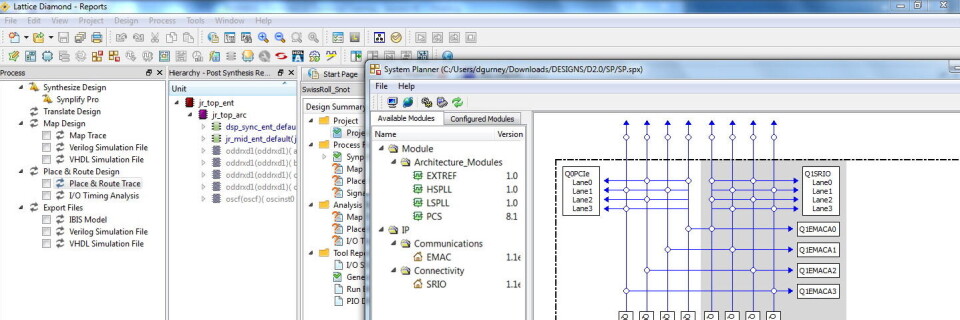

Utviklingsmiljøet skal gjøre det mulig å utforske designalternativer under utvikling av FPGA-applikasjoner, og inkludererer støtte for timing, effekt og pakking basert på tidlig silisiumkarakterisering av LatticeECP4-190 komponenten. Foruten algoritmer som bidrar til å sikre lav kost og effekt, kommer programmet med et nytt System Planner verktøy som gjør at brukerne kan dra nytte av de tolv 6Gbps SERDES kanalene som tilbys i LatticeECP4 enhetene.