Setter fart på dataflyten

Altera utvider nå sin lavkost FPGA-serie med Cyclone IV, som de tror kan håndtere den stadig økende datamengden i mange produkter, og kanskje erstatte ASIC- og ASSP-baserte løsninger.

Denne artikkelen er 2 år eller eldre

Altera Cyclone IV kommer i to familier, en med transceivere (GX) og en rimeligere, laveffekt versjon (E). – Vi tror Cyclone IV kan løse mange problemer innen alt fra trådløse enehter til industrielt ethernet, 3D skjermer (!) og kringkasting, kommenterer produktsjef Bob Blake i Altera.

Transceiverprotokoller

Nytt er blant annet støtte for alle de vanligste transceiverprotokollerne (SDI, GigE, CPRI, V-by-One, SATA osv.) og en kjerneteknologi som er direkte rettet mot de ulike applikasjonene. – Poenget er at man skal komme raskt i gang, og ha en rask vei mot volumproduksjon, sier Blake. – Designeren skal slippe å lete etter IP. Derfor har vi bl.a. hard IP for PCI Express (PCIe) innebygd, påpeker han.

Størst og minst

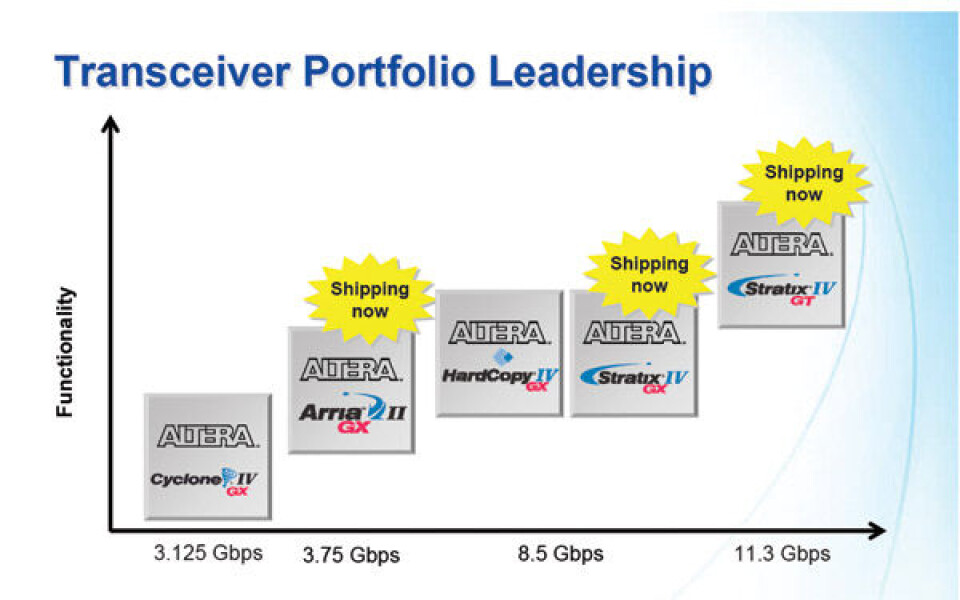

Cyclone-familien ble introdusert i 2002, og tok skikkelig av med Cyclone III, som ble introdusert i 2007. Ifølge Blake er det levert mer enn 120 millioner komponenter. Cyclone IV GX har opptil 150k logiske elementer (LE), opp til 6,5 Mb med RAM, maks 360 multiplikatorer og opp til åtte integrerte, 3,125 Gb/s transceivere. Den blir også den minste FPGAen på markedet med transceivere - minste størrelse er 14k logiske elementer og to transceivere. I den andre enden av skalaen er forøvrig også en GT-versjon av Stratix på vei ut, med 11,3 Gb/s transceivere! Bare så det er nevnt.

Besparelser

– Disse FPGAene kan gi betydelige plass- og strømbesparelser for integrasjon av I/O. Dessuten trenger de kun to strømkilder, sier Blake. Han viser som et eksempel et videoinnhentingskort for kringkasting, der man har kunnet integrere PCIe og SDI I/O med hjelp av en FPGA. Man kan også tenke seg eksempler der man erstatter en ASSP og/eller ASIC med en Cyclone IV.