Åpen maskinvare:

En god strategi for mikrokontroller-utvikling

En rivende utvikling av åpen kilde-baserte byggeklosser og utviklingsmiljø for mikrokontrollere åpner nye muligheter.

Mikrokontrollere (MCUer) er hjertet i de fleste enheter som er koblet til tingenes internett (IoT). De utgjør dermed en bærebjelke i mange av dagens industrielle IoT-løsninger og elektroniske produktstrategier. De fleste mikrokontrollere på markedet er basert på prosessorkjerner med en eller annen form for RISC-arkitektur, med Arm og AVR som de mest utbredte alternativene. Imidlertid er det stadig flere organisasjoner som tyr til åpen maskinvare i stedet for disse leverandøreide teknologiene.

Åpen kilde

Økosystemet av prosessorkjerner, mikrokontrollere, innvevde datamaskiner, sensorer og aktuatorer med åpen kilde er stadig voksende. Siden maskinvaren har stor innflytelse på utformingen av IoT-løsninger, ser utviklerne klare fordeler ved å bruke komponenter med åpen kilde. IoT-utviklere optimaliserer koden sin for størrelse og trenger ofte å holde strømforbruket på et minimum, særlig når det gjelder enheter som skal benyttes ute i felt. Det er enklere å oppnå ønsket strømprofil når du har kontroll over både programvaren og maskinvaren. Maskinvare med åpen kilde bidrar også til å sikre en stabil maskinvareplattform gjennom hele løsningens livssyklus. Hvis én leverandør ikke lenger kan levere en komponent, er det alltid mulig å finne en annen. Sist, men ikke minst, gjør åpen maskinvare det mulig for utviklerne å utvide og forbedre komponentene. Siden løsninger for loT og kantprosessering ofte brukes på avsidesliggende steder og i krevende miljøer, er muligheten til å tilpasse maskinvaren til det aktuelle bruksområdet uvurderlig.

RISC-V

RISC-V er et utmerket eksempel på en åpen arkitektur som er på full fart inn. Det finnes til og med åpne kilder for kjerne- og mikrokontrollerdesign, for eksempel OpenHW CORE-V MCU. RISC-V-arkitekturen ble introdusert i 2010 av forskere ved University of California i Berkeley, og er en åpen standard. Dokumentene for instruksjonssett-arkitekturen (ISA) er publisert under åpen kildelisens, og det samme gjelder flere kjernedesign. RISC-V Foundation ble dannet i 2015 for å forvalte utviklingen av ISA; organisasjonen flyttet til Sveits i 2019 på grunn av utfordringer med amerikanske handelsregler og tok navnet RISC-V International fra mars 2020.

Betydelig utbredelse

RISC-V International tillater ubegrenset bruk av ISA i maskinvare og programvare. Denne tilnærmingen har resultert i en betydelig utbredelse. I mars 2022 var 111 ulike kjerner, 31 SOC-plattformer og 12 SOC-er oppført på organisasjonens nettsted. Den faktiske utbredelsen av RISC-V er sannsynligvis mye høyere, siden ikke alle organisasjoner offentliggjør at de bruker teknologien. Det er verdt å nevne at bare medlemmer av RISC-V International har stemmerett for å godkjenne endringer og kan bruke den varemerkede kompatibilitetslogoen.

Modularitet

Et viktig kjennetegn ved RISC-V ISA er modulariteten. Det grunnleggende instruksjonssettet for heltall er tilgjengelig i 32-bits og 64-bits format (RV32I og RV64I). Det finnes utkast til en innebygd 32-bits versjon (16 registre, RV32E) og til og med en 128-bits versjon (RV128I). Alle andre typer instruksjoner er dokumentert i standardutvidelser for ISA. Disse utvidelsene har vanligvis en enkelt bokstav som navn, selv om de nyeste har et navn som begynner med Z etterfulgt av et alfabetisk navn. Velkjente eksempler på standardutvidelser er multiplikasjon og divisjon av heltall (M), atominstruksjoner (A), flyttall med enkel presisjon (F), flyttall med dobbel presisjon (D) samt kontroll- og statusregister (Zicsr). Standardutvidelsene er utformet slik at de fungerer sammen med alle standard basisinstruksjonssett og ikke er i konflikt med hverandre. Utviklere av RISC-V-kjerner kan også lage sine egne ikke-standardiserte utvidelser av instruksjonssettet. Det har dessuten begynt å dukke opp initiativer til industrisamarbeid om brukerdefinerte utvidelser.

Utvidelser

Et godt eksempel er OpenHW CORE-V eXtension 1/F, som har som mål å forenkle implementeringen av egendefinerte instruksjoner og akseleratorer som er knyttet til eller innebygd i RISC-V-kjerner. RISC-V-spesifikasjonen fastslår at slike utvidelser må ha et navn som begynner med X for instruksjoner på brukernivå og SX for instruksjoner på overordnet nivå. Det er dermed vanskelig å kartlegge hele RISC-V-landskapet. Dette skyldes at de som implementerer RISC-V kan designe kretsene sine fra bunnen av, ta i bruk en av de mange åpne kjernene som er tilgjengelige, eller til og med lisensiere åpne eller kommersielle kjerner og legge til proprietære funksjoner.

Mangfoldig

På den ene side gjør dette økosystemet mangfoldig, med kjerner, mikrokontrollere og SOC-er som kan integreres i kompakte enheter, gatewayer, kant-noder samt, i økende grad, maskinvare i desktop- og serverklassen. På den annen side er det vanskeligere å gi et overordnet bilde av markedet, ettersom produktene mangler felles referansepunkter. Ikke desto mindre finnes det et blomstrende økosystem av RISC-V-baserte mikrokontrollere, og de er utvilsomt verdt å vurdere. Selv etablerte aktører i Arm-markedet tilbyr nå produktserier basert på RISC-V.

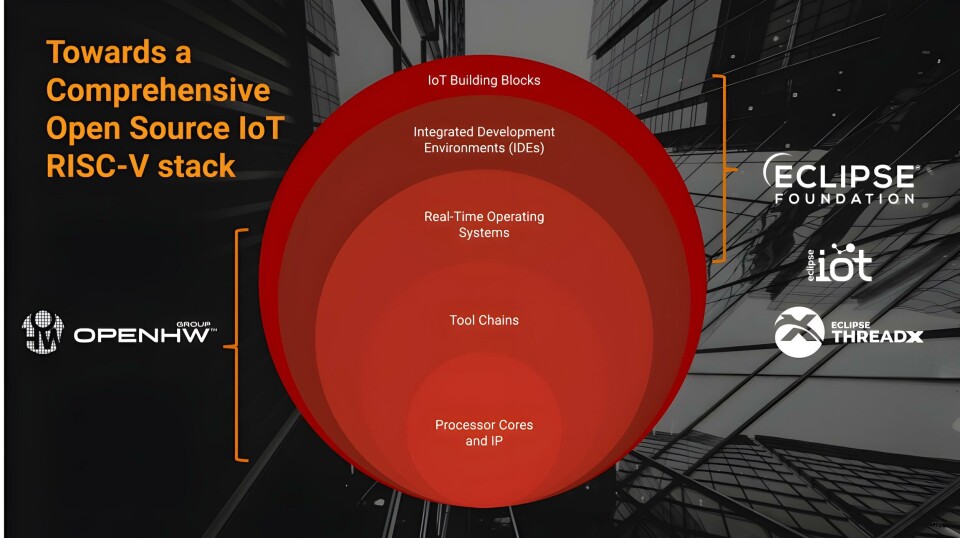

Eclipse og OpenHW Group får det hele til å fungere sammen

Eclipse Foundation, en av verdens største åpen kilde-stiftelser, samarbeider tett med OpenHW Group for å bygge et omfattende RISC-V-økosystem basert på implementeringer av prosessorkjerner med åpen kilde. OpenHW Group er en global ideell organisasjon basert i Canada, der maskinvare- og programvaredesignere samarbeider om å utvikle prosessorkjerner med åpen kilde, tilhørende IP, verktøy og programvare. Alle elementer i OpenHW-økosystemet utvikles i offentlig tilgjengelige GitHub-repoer. Kjernedesignene er definert i SystemVerilog og er lisensiert under Solderpad Hardware-lisens versjon 0.51. Denne lisensen er basert på Apache-lisens 2.0 og legger til rette for kommersiell bruk.

Utvikler mikrokontroller

I skrivende stund tilhører alle OpenHW-kjernene CORE-V-familien. På et overordnet nivå kan CVA-familien av CORE-V-prosessorer brukes i gatewayer og edge-noder, mens CVE4-familien, som har tre forskjellige kjerner, er rettet mot kjerner i mikrokontroller-klassen. Et godt eksempel på denne tilnærmingen er OpenHW Group CORE-V MCU-prosjektet, som tar sikte på å utvikle en mikrokontroller basert på CV32E40P-kjernen. Mikrokontroller-enheten har blant annet støtte for 12C, PWM, SPI og UART.

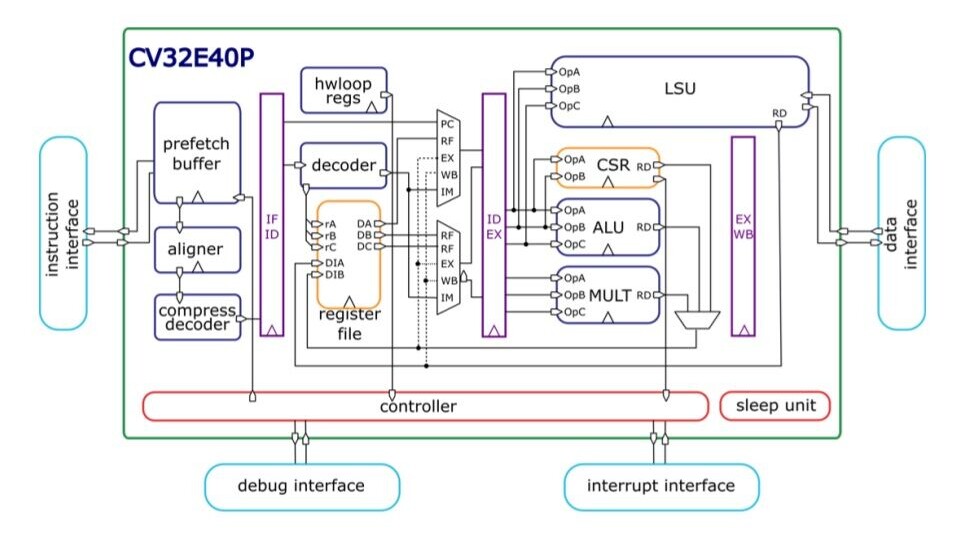

Fra et teknologi-perspektiv har CV32E40P-kjernen følgende egenskaper:

- 32-bits (RV32I), 4-trinns, in-order, single-issue

- Standard RISC-V-utvidelser: F, I, M, CZicount, Zicsr, Zifencei

- Egendefinerte utvidelser: PULP_XPULP, PULP_CLUSTER, PULP_ZFINX

- M-modus, CLINT, OBI

- Avbrudd og feilsøking

Diagrammet nedenfor illustrerer den interne strukturen i CV32E40P.

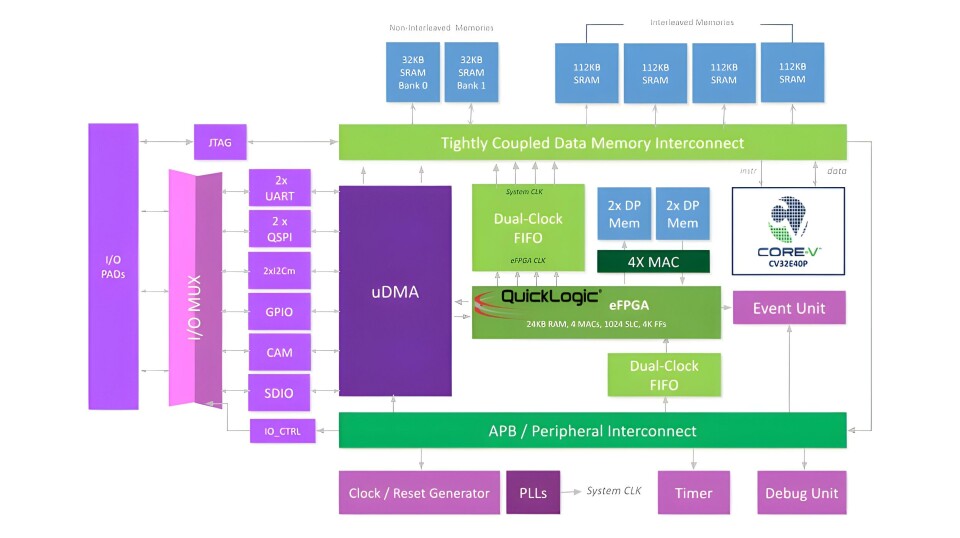

En kjerne alene er naturligvis ikke nok til å støtte applikasjoner i den virkelige verden. Derfor startet medlemmene i OpenHW-fellesskapet CORE-V MCU-prosjektet. Målet var å utvikle en mikrokontroller med alle funksjoner som kan støtte et bredt spekter av innebygde applikasjoner. CORE-V er en perfekt plattform for å distribuere applikasjoner som bygger på de populære sanntidsoperativsystemene FreeRTOS og Eclipse ThreadX.

Mikrokontrolleren CORE-V har følgende funksjoner:

- ~400+MHz CV32E4 MCU

- Innebygd FPGA-struktur med maskinvareakseleratorer fra QuickLogic

- Flere kontaktpunkter med lavt strømforbruk for periferienheter (SPI, GPIO, I2C, HyperRAM, CAMIF osv.)

Dette diagrammet viser hvordan CORE-V-mikrokontrolleren omgir CV32E40P-kjernen med nyttige periferienheter og I/O-kanaler:

Utviklingsmiljø

Nå lurer du kanskje på hvor Eclipse Foundation og stiftelsens åpen kilde-prosjekter passer inn i dette bildet? Svaret er enkelt: verktøy og byggeklosser. Ett av OpenHW Group-prosjektene er CORE-V IDE, et integrert utviklingsmiljø som er forhåndskonfigurert for å tilby CORE-V-brukere alt de trenger for å benytte CORE-V-maskinvaren på en effektiv måte. CORE-V IDE er et sett med programtillegg som kjører på det velprøvde Eclipse IDE. OpenHW-gruppens programvaregruppe arbeider selvfølgelig også med verktøy på lavere nivå, for eksempel en kompilator, som muliggjør støtte for CORE-V-plattformen.

IoT-byggeklosser

Eclipse Foundation handler imidlertid om mye mer enn Eclipse IDE. Eclipse IoT-arbeidsgruppen tilbyr et sett med IoT-byggeklosser som utfyller innebygde applikasjoner. I november 2023 bidro Microsoft dessuten med Azure RTOS til Eclipse Foundation, og ga dermed støtet til Eclipse ThreadX-prosjektet. ThreadX er et modent sanntidsoperativsystem fra 1997. Det er det første og eneste RTOS-et med åpen kildekode som er sertifisert for sikkerhetskritiske applikasjoner. ThreadX støtter ulike plattformer, inkludert noen få kjerner basert på RISC-V ISA. Partnerskapet mellom Eclipse Foundation og OpenHW Group er på vei inn i en ny fase, og kombinasjonen av CORE-V og ThreadX skaper utallige muligheter for bruk av åpen maskinvare innen sikkerhetskritiske systemer.