Rendyrker embedded-segmentet

EmLogic er etter ett års drift på stø kurs til å bli et senter for embedded – innvevd elektronikk – i Norge. Samtidig opplever de suksess for verifikasjonsløsningen UVVM.

Denne artikkelen er 2 år eller eldre

For et år siden etablerte EmLogic seg som en ny aktør innen innvevd elektronikk, og samlet raskt de tekniske lederne fra tidligere Bitvis. Den gang ble det uttalt at de ikke skulle vokse for mye, men allerede er bemanningen økt fra 1 til 21 ansatte, med flere på vei inn.

Heftig vekst

– Veksten har vært heftig, medgir daglig Espen Tallaksen, som mener det har sammenheng både med et godt marked og ikke minst god markeds- kjennskap. – Dessuten kan vi nå levere flere tjenester innen fagfelt som maskinvare og DSP i tillegg til programvare og FPGA, fremholder han.

Tilbyr flere fagfelt

Parallelt med at markedet går godt, skulle man tro at kompetansemangel ville gjøre seg gjeldende for et firma i vekst, men ifølge Tallaksen har man vært «heldig» og fått tak i de riktige folkene. – En viktig faktor er nok også at mange kjenner oss, at vi har et sterkt fokus på designmetodikk, og ikke minst at vi har en policy med vesentlig eierskap for de ansatte i bedriften, sier han.

Designmetodikk – UVVM

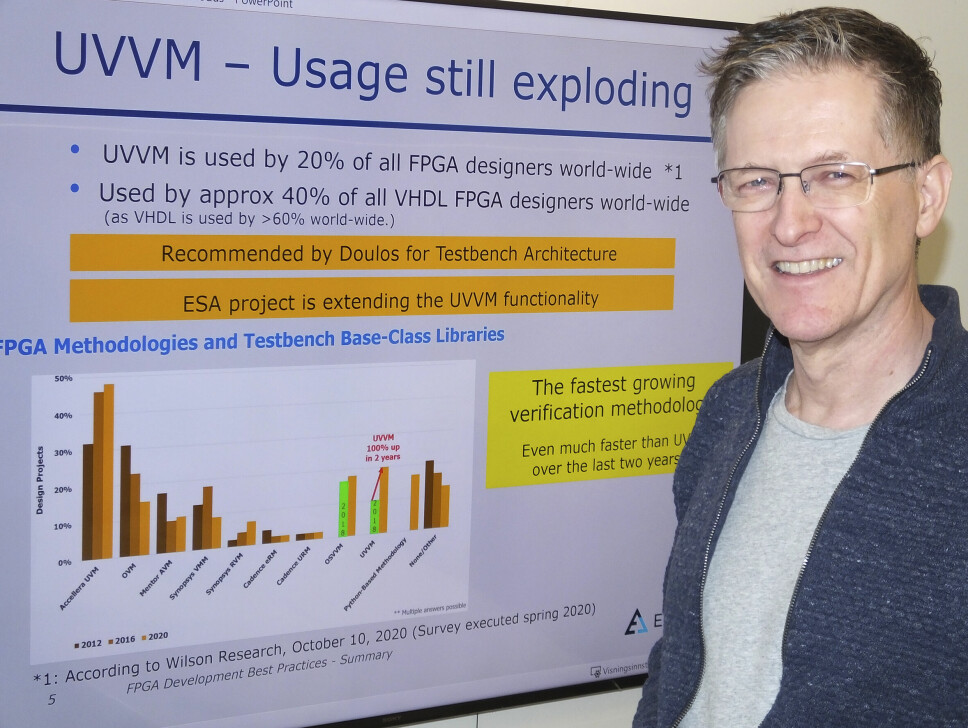

Apropos designmetodikk, så har EmLogic fått stor suksess med sin åpne verifikasjonsmetodikk (og -bibliotek) UVVM – Universal VHDL Verification Methodology, som de vedlikeholder i samarbeid med Inventas. Løsningen beskrives som en meget strukturert infrastruktur og arkitektur som skal forbedre verifikasjonseffektiviteten betydelig. Blant viktig innvirkning på utviklingen er bedre designkvalitet og enklere gjenbruk av verifikasjonskomponenter. UVVM er anbefalt av Doulos for testbenkarkitekturer, og blir ofte anbefalt i nye prosjekter i regi av den Europeiske Romfartsorganisasjonen, ESA!

Åpen kilde

Tallaksen opplyser at UVVM adopteres i rask takt av stadig flere EDA- leverandører. Ifølge Wilson Research Group er det allerede det mest brukte i verden for VHDL-verifikasjon og nummer to uavhengig av språk – og raskest voksende. I fjor ble UVVM del av «IEEE Standards Association for Open Source Projects».

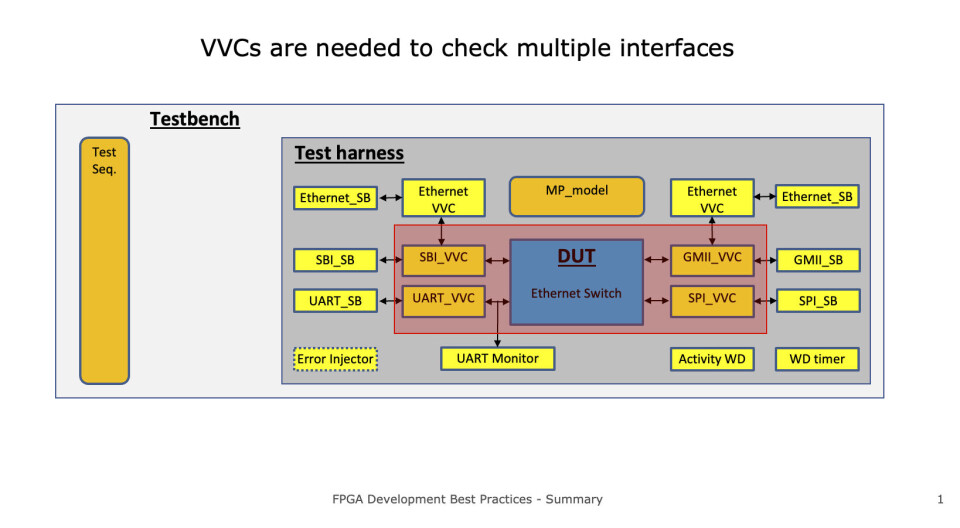

For all HDL-verifikasjon er det nemlig viktig å ha en meget strukturert testbenkarkitektur, å kunne kontrollere aktivitet på flere grensesnitt samtidig, tillate gjenbruk og gjøre det mulig å styre testbenken fra én enkelt sekvenser.

Simulering viktig

– Bruk av testbenk og simulering generelt er viktig blant annet for å gjøre det enklere og billigere å reparere ting tidligst mulig. Vi ser også at det er blitt ekstremt mye mer fokus på verifisering gjennom de siste 10 årene, sier han. – Med denne løsningen kan du få mer kontroll, raskere iterasjoner og ha mer strukturerte, bottom-up verifikasjon. For eksempel kan du singel-steppe gjennom testbenk og design for å sjekke hva som skjer, forklarer Tallaksen engasjert. – Du kan til og med finne «bugs» som du trolig ikke ville ha funnet på laben under test – for ikke å snakke om sjeldne tilfeller som kan oppstå, legger han til.

Ingenting for stort

I enkelte miljøer snakker man om at dagens FPGAer er blitt for store til å kunne verifiseres. – Det er en totalt feil innfallsvinkel, mener Tallaksen. – Det aller meste kan verifiseres. Derimot bør man alltid ta et aktivt valg på hva som er mest fornuftig å verifisere med simulering versus å teste på laben, fastslår han. Noe som kan koste endel tid verifiseringsmessig er å håndtere «hjørnetilfeller» og ting som skjer samtidig. Et eksempel på et datahjørnetilfelle kan være dersom en UART (universal asynkron sender/mottagergrensesnitt) får nye data fra mottagerpinnen (Rx) samtidig som den får en leseforespørsel på en tidligere byte. Og så videre. For hjørnetilfeller er simulering klart best.

VVC

En viktig del av UVVM er de såkalte strukturerte verifikasjonskomponentene, VVC. Verifikasjonskomponentene utgjør en standard måte å bygge blokker som kan utføre oppgaver på instruksjoner fra testsekvenseren, og det finnes et stort bibliotek av verifikasjonskomponenter, inkludert for en mengde ulike grensesnitt, f.eks. AXI, Avalon, UART m.fl.

Finne feil effektivt

Ifølge tidligere nevnte undersøkelse fra Wilson Research Group brukte utviklere i 2020 mer enn 50% av tiden under FPGA-utvikling på verifikasjon. Halvparten av verifikasjonstiden igjen ble brukt på debugging: Design, testmiljø og testcase. – Dette indikerer at man har testsystem som ikke finner feil på en effektiv måte. Derfor er det uhyre viktig å lage testsystemer for effektiv debugging, sier Tallaksen. – Og hvis du bruker litt mer tid på å skrive oversiktlig og lesbar kode, sparer du masse tid senere, understreker han.

Enorme tidsbesparelser

Ifølge Tallaksen er det mulig å spare fra 100 til 1000 timer (av en total på 3000) i lav- og middels komplekse prosjekter ved å bruke UVVM. I større prosjekter, enda mer. I tillegg kommer positiv innvirkning på time-to-market og ikke minst feilrate (MTBF).

Videreutvikling

Forløperen til UVVM så dagens lys allerede for nesten 20 år siden, i det såkalte Embla-prosjektet for WesternGeco. Den første kommersielle versjonen, Digitas Utility Library, kom i 2008. Siden har utviklingen gått sin gang, under flere firmanavn. ESA har allerede inngått samarbeidsavtale om videreutvikling av UVVM i to prosjekter og Tallaksen er nå i samtaler med ESA om et tredje prosjekt.

Romfart-drevet

– ESA har vært viktig for utviklingen og utbredelsen av UVVM, og har forsvart ressursbruken, som har vært enorm. Samtidig gir selvsagt ESA voldsom kredibilitet i utviklingsmiljøer, fremholder Tallaksen, som understreker at både EmLogic og UVVM er inne i mange flere markeder enn bare romfart, inkludert industri, offshore, medisin og kommersielle høyvolumprodukter.